Renesas and INCHRON have joined forces to create a combined solution that helps customers to create reliable and fast dynamic architectures and applications.

1. Optimize System & Software Architecture by Timing Simulation

Users of Renesas products build applications that are real-time critical or have real-time critical parts. Taking care of the dynamic behavior and making timing and performance predictable is critical to the success of a project.

System and software architects use the INCHRON Tool-Suite and knowledge of the INCHRON experts to create an architecture and design that fits both function and timing requirements.

Using a model-based simulation approach allows architects to evaluate different architecture variants and to verify timing & performance requirements early in the project. This reduces risks and costs of late errors.

Architects use the model-based simulation approach on all architectures levels.

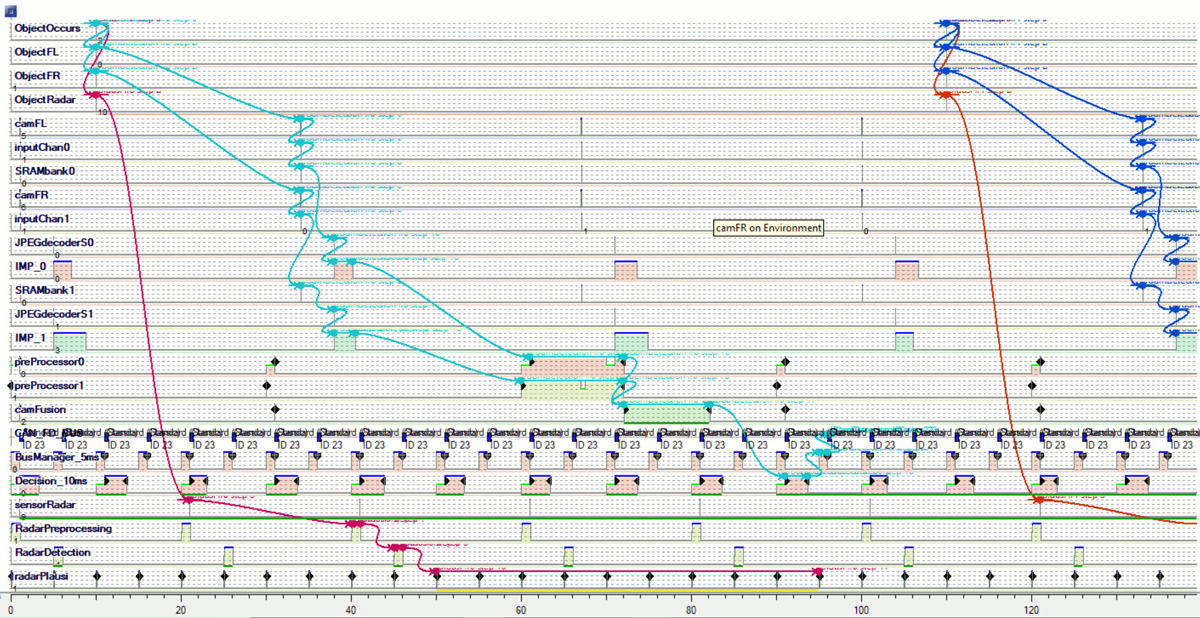

Event chains describe the data flow from sensors via data processing units to actuators. Using an event chain focused approach enables architects to reduce the complexity of their projects.

Typical application areas are HPCs for automated driving and ADAS, as well as engine, chassis and body systems in vehicles. Any other system, that is real-time critical is well suited, too.

Questions from the following areas can be evaluated:

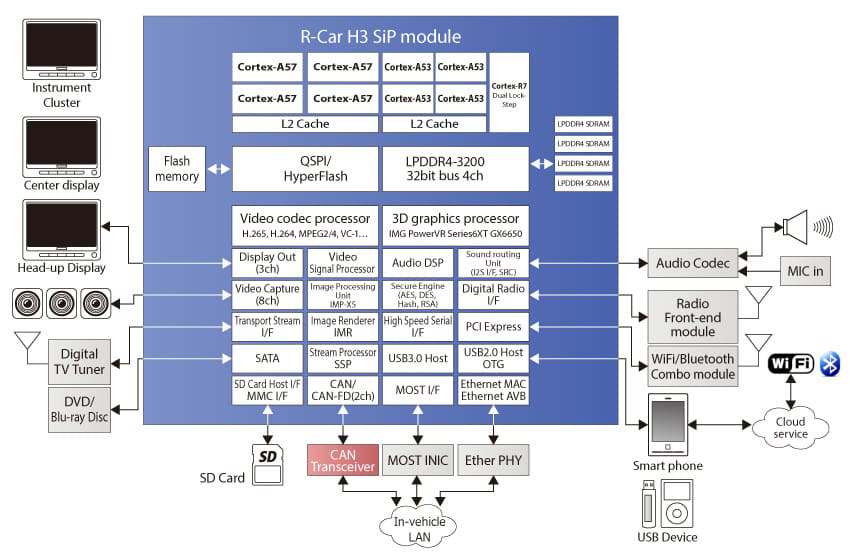

Hardware / software co-design, efficient use of cores, resources consumption, communication delay, bandwidth and memory load, efficient use of IP cores and interaction with other cores, etc.

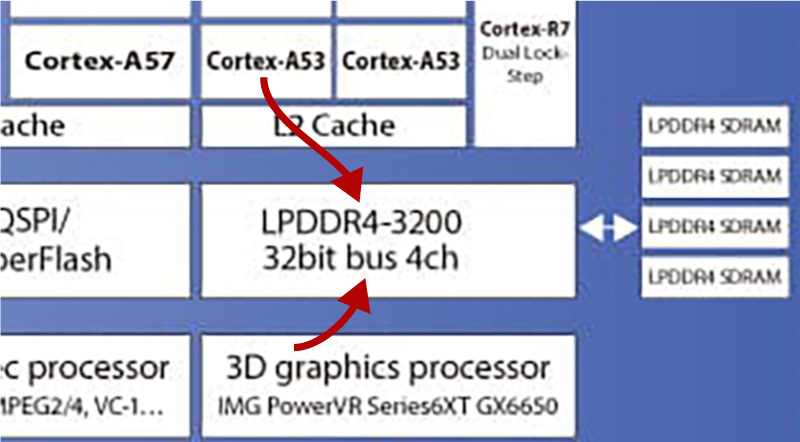

In Renesas R-Car many parallel running cores use the only available DRAM. Access conflicts and bus congestion can lead to higher execution times, because of wait states. The memory bandwidth utilization can be simulated to optimize the overall performance.

Features

- For all Renesas platforms (R-Car, RH850, etc)

- All RTOS / all operating systems: AUTOSAR classic und AUTOSAR adaptive platform, QNX, Linux, hypervisor

- Multi-core, Multi-CPU, Many-core, all communication interfaces

- Service oriented communication

2. Understand System & Software Dynamic Behavior by Trace Analysis

Analyzing the real-time behavior and performance is an important step during the development of a project.

Engineers have to make sure that the desired performance is within required limits and they have to continuously monitor the performance.

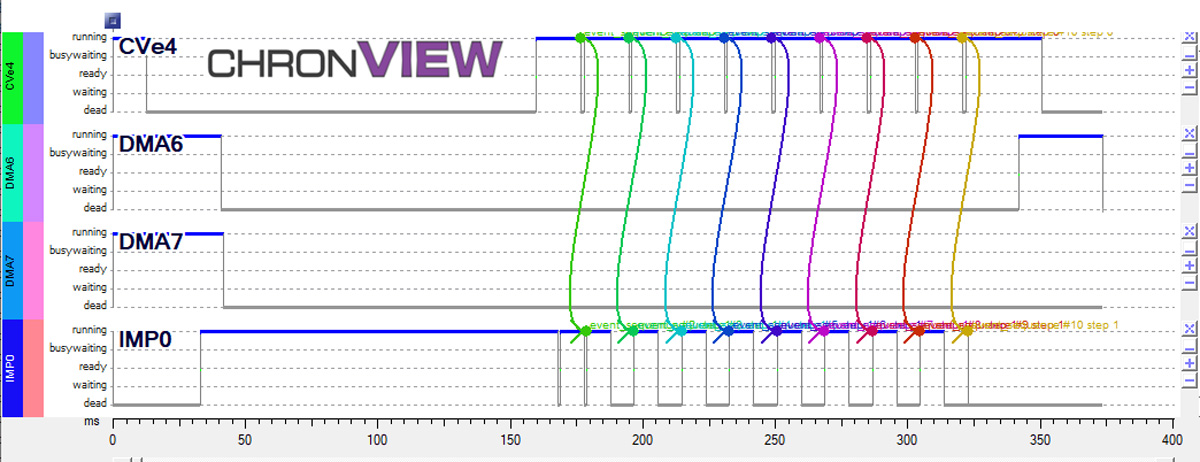

The INCHRON Tool-Suite can visualize traces taken with Renesas tools or 3rd party tools. It shows deep insight into timing behavior, allows engineers to analyze the current state and help them find optimization ideas.

You benefit especially from the evaluation of timing requirements (both from simulation and traces) and visualization of event chains.

Tracing on Renesas silicon

- Hardware sources(via ARM CoreSight): ARM CortexA, ARM CortexR, Renesas IP (e.g. IMP, IMR), interconnect

- Hardware trace tools: Lauterbach, iSYSTEM, PLS,…

- Renesas trace tools

- OS trace tools: LTTng, QNX traces, Integrity traces,…

- Custom trace tools and transport protocols e.g. DLT

When monitoring a system in many cases traces are recorded in parallel from different sources and with different tools. INCHRON’s trace merge solution allows merging multiple traces files into one cross-core/cross-OS trace. This allows visualizing and analyzing the behavior of the overall system.

Automation interfaces like batch mode and Python API allow integration with build tools. So traces can be checked against requirements and reports can be generated fully automatically.

3. Use Cases

Renesas and INCHRON cover a variety of use cases. Each use case includes a model and example files.

3.1 Renesas R-Car Gen 3 Model

What is the timing of my event chains?

INCHRON provides:

- Multi-path image processing example application

- Modell templates for R-Car Gen 3

- ARM A53, R7 and IMP involved

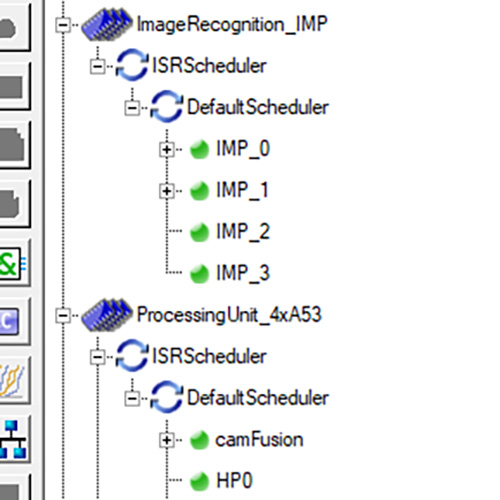

3.2 Efficient Deployment to Application Cores and Hardware Accelerators

What is the best balance between IP cores and ARM applications?

INCHRON supports the architecture process:

- deployment to ARM cores, IMP and CNN IP

3.3 Memory Bus Load

How can I schedule my overall system to reduce peak memory load?

INCHRON provides:

- Simulation of memory bus load for large data volumes

- Sources: ARM cores, IMP, CNN, further IP cores

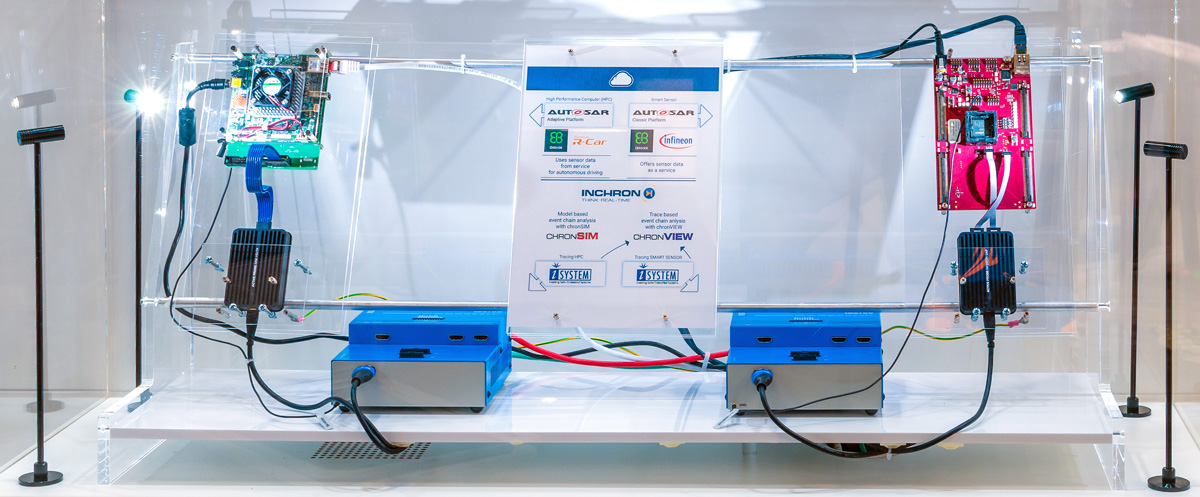

3.4 AUTOSAR classic & adaptive platform with service oriented communication

How can AUTOSAR classic platform and AUTOSAR adaptive platform systems work together?

INCHRON provides an example with:

- Renesas R-Car with AUTOSAR adaptive platform

- Smart sensor with AUTOSAR classic platform

- Service oriented communication

- with Elektrobit Tresos, Elektrobit Corbos, iSystem

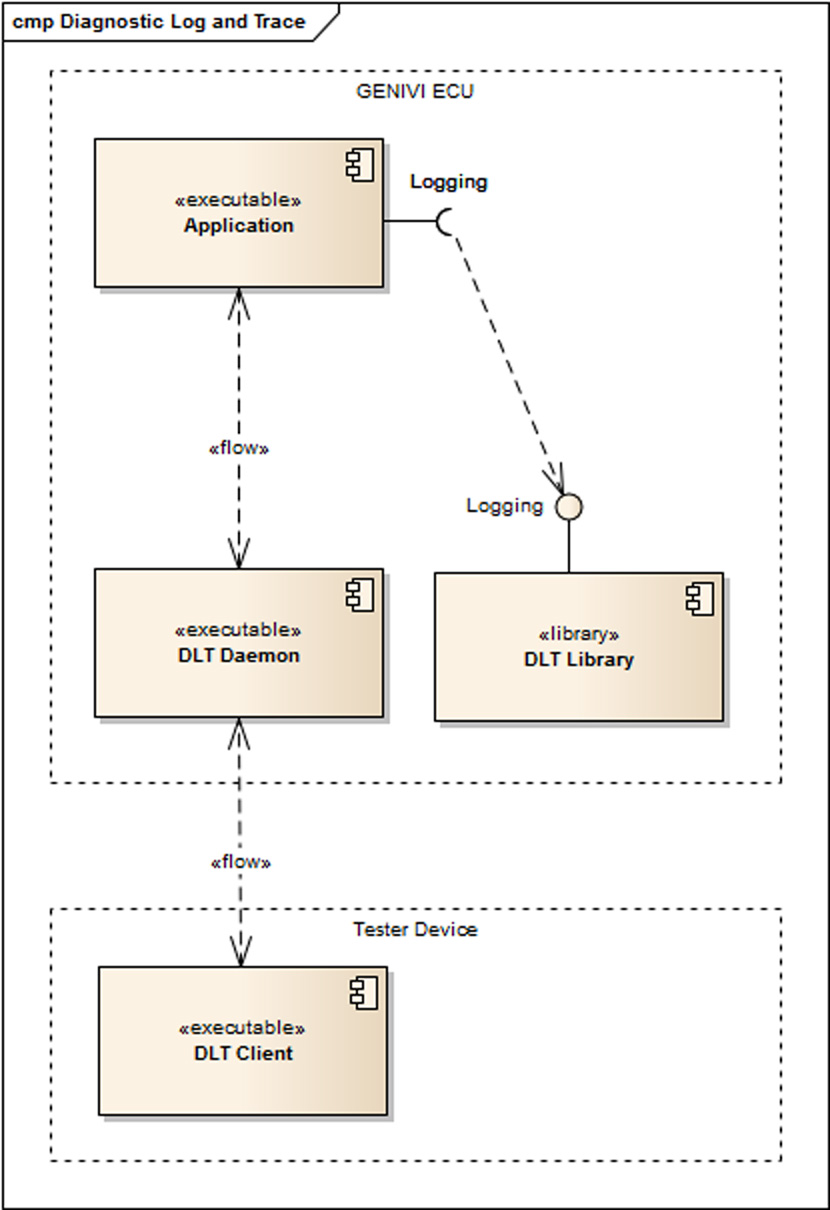

3.5 Renesas R-Car Linux Diagnostic Log and Trace (DLT)

How can I trace the Renesas R-Car?

INCHRON supports tracing with:

- Diagnostic Log and Trace (DLT) Trace on R-Car with Linux / AUTOSAR adaptive platform

- Instrumented example Linux application

3.6 Renesas RH850 multi-ECU with hypervisor

How can I trace multiple boards? How can I trace a hypervisor environment?

INCHRON provides an example setup with:

- 3x RH850

- Hypervisor OpenSynergy COQOS micro on each board

- Trace with iSYSTEM